Lena Zeitlhöfler published a new paper:

Simulation of the Transient Potential Distribution On-Chip During a Fast ESD Event Based on a Parametric Measurement Analysis

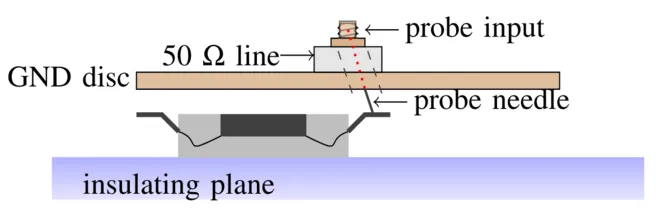

ESD events on semiconductor devices in the pico-or nanosecond range cause local potential differences and are often responsible for severe damages of an IC. The presented simulation approach focuses on the simulation of the transient and local potential distribution on the chip during a discharge on wafer-level. In the approach, the total charge is distributed either via the top metal layer and also via the underlying substrate layer dependent on the IC design. The approach consists of a network-based simulation with uniform cells of lumped elements, which values are determined based on measurement data.

the paper can be accessed here: https://ieeexplore.ieee.org/abstract/document/9245864