## Entwurf und Implementierung eines Multi-Bit-parallelen Level-Crossing ADC

Masterarbeit am Lehrstuhl für Schaltungsentwurf (kann mit einem Forschungspraxis am Lehrstuhl kombiniert werden)

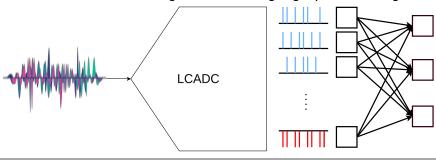

Im Zusammenhang mit intelligenten Sensorsystemen ist die Spike-Codierung von Audiosignalen von großem Interesse für die Entwicklung von Spiking Neural Networks (SNN). Eine vielversprechende Methode der Umwandlung von (analogen) Daten in Spikes sind Level-Crossing ADCs (LCADCs). Diese ereignisgesteuerten Schaltungen tasten das Eingangssignal nur spärlich ab und sparen dadurch in Phasen geringer Aktivität Energie. In Phasen hoher Aktivität leiden die meisten LCADCs jedoch unter einer Slew-Rate Limitierung am Eingang was eine Schaltung mit relativ hoher Geschwindigkeit erfordert, um dem Eingangssignal zu folgen. Bei einer Auflösung von  $\bf n$  Bits benötigt ein LCADC  $\bf 2^n$  Schritte, um den gesamten Eingangsbereich zu durchlaufen, da jeder Spike eine Signaländerung von einem  $\bf U_{lsb}$  darstellt.

Die Hauptaufgabe dieser Arbeit besteht darin, einen bestehenden LCADC so umzugestalten, dass er mehrere binär gewichtete Ausgangsspitzen ermöglicht.

Ihre Arbeit besteht aus dem Entwurf und der Implementierung des vorgeschlagenen Designs im 22nm GF-Node. Sowohl das analoge als auch das digitale Schaltungsdesign wird mit den entsprechenden Cadence Design Tools am Lehrstuhl durchgeführt. Sie werden zunächst eine wissenschaftliche Literaturrecherche zum Stand der Technik von LCADCs im Kontext von SNNs durchführen. Es steht Ihnen dann frei, das bestehende Design so anzupassen, dass es den Anforderungen entspricht oder eine eigene Idee von

Kenntnis der folgenden Themen und Software ist hilfreich, aber nicht notwendig:

- · Analoger/Digitaler Schaltungsentwurf

- Virtuso, genus, Innovus

- Verilog/VHDL

Grund auf zu realisieren.

- ADCs

- (Spiking) Neural Networks

Interessiert? → Kontakt: Kilian David kilian.david@tum.de Raum N5301