## Miniaturisierte FIR Filter mit erhöhter Präzision durch stochastische Sign-Magnitude Arithmetik

Gayas Mohiuddin Sayed und Matthias Kuhl

Professur für Mikroelektronik, Institut für Mikrosystemtechnik - IMTEK

Albert-Ludwigs-Universität Freiburg, Deutschland

Email: gayas.sayed, matthias.kuhl@imtek.uni-freiburg.de

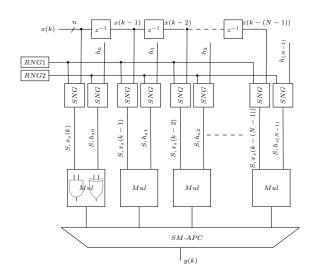

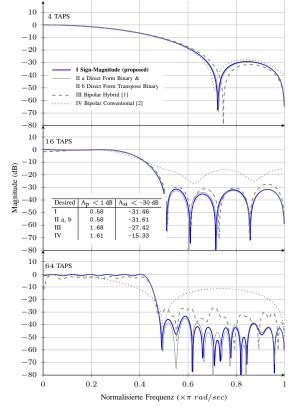

Abstrakt- Dieser Beitrag stellt eine Stochastisch-Binäre Hybrid Architektur zur Miniaturisierung von FIR-Filtern und deren Vergleich mit etablierten Implementierungen von Filtern vor. Die FPGA-Realisierung von 4-, 16- und 64-TAP-FIR-Filtern mit 8-Bit Wortlänge bestätigt den Nutzen der vorgeschlagenen Architektur in hochkompakten Systemen. In einem 4- TAP FIR Filter, mit der vorgeschlagenen Architektur werden die FPGA Ressourcen um ~ 53% reduziert, wobei die Flächeneffizienz mit steigender Filterordnung zunimmt. Diese hybride Architektur mit Multiplikation in der stochastischen und Akkumulation in der binären Domäne erfordert nur 2 Zufallszahlengeneratoren, einen für die Verzögerungsleitungen und den anderen für die Filterkoeffizienten. Dank sogenannter "low-discrepancy" Sequenzen basierend auf Additive-Recurrence in stochastischen Zahlengeneratoren und unskalierter Binär-Akkumulation, erzielt die vorgeschlagene stochastische Architektur Best-in-Class-Performance. Dies wird anhand einer detaillierten Analyse eines Filters mit 16- TAP validiert, welcher eine Durchlasswelligkeit von  $A_p = 0.58 \, dB$  und eine Sperrdämpfung von  $A_{st} = -31.46 \ dB$  erreicht, wobei keine Qualitätsunterschiede zu binären Implementierungen zu erkennen sind. Zusätzlich wird ein mathematischer Ansatz vorgestellt, um den Fehler in der Filterausgabe lange vor der eigentlichen Implementierung abzuschätzen. Die ASIC-Synthese eines FIR-Filters mit 16 TAP basierend auf der vorgeschlagenen Architektur erreicht eine Fläche von  $30,165 \mu m^2$ und ist allen diskutierten Filterstrukturen überlegen. Das Filter gewährt 68% Flächenreduktion im Vergleich zu der binären Implementierung und hat einen Energieverbrauch von  $0.429 \, nJ$  pro Operation, ein Wert, der mindestens 1.8× niedriger ist als bei früheren stochastischen Designs liegt.

Fig. 1. Vorgeschlagene Sign-Magnitude Stochastische FIR-Filterarchitektur

TABLE I  $16\text{-TAP FILTER VERGLEICH IN }180\ nm\ \mathsf{CMOS}\ \mathsf{TECHNOLOGIE}$

| Struktur                     | A <sub>st</sub> | Fläche     | Strom <sup>(*)</sup> |

|------------------------------|-----------------|------------|----------------------|

|                              | < -30  dB       | $\mu m^2$  | $\mu W$              |

| Sign-Magnitude (vorschlagen) | -31.46          | 30,165     | 268                  |

| Direct Form Binary           | -31.61          | 95,096     | 549                  |

| Direct Form Transpose Binary | -31.61          | 108,691    | 600                  |

| Bipolar Hybrid [1]           | -27.42          | $51,\!276$ | 375                  |

| Bipolar conventional [2]     | -15.33          | 33,208     | 243                  |

\* Dynamische Leistung bei 20 MHz Takt und 1,2 V Versorgung.

Fig. 2. Normalisierter Frequenzgang der diskutierten Implementierungen

## QUELLENANGABE

- S. Koshita, et al., "High-accuracy and area-efficient stochastic fir digital filters based on hybrid computation," *IEICE Transactions on Information* and Systems, vol. E100.D, no. 8, pp. 1592–1602, 2017.

- [2] R. Wang, et al., "Design, evaluation and fault-tolerance analysis of stochastic fir filters," *Microelectronics Reliability*, vol. 57, pp. 111–127, 2016