# New materials on horizon for advanced logic technology in mobile era

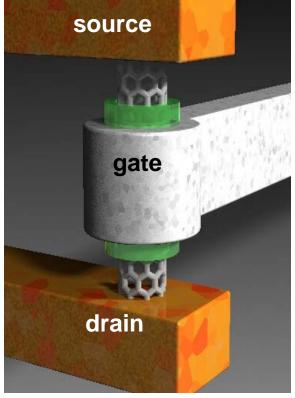

Franz Kreupl, IFX 2003

Hsinchu – March 6, 2013 - Prof. Dr. Franz Kreupl

# Outline

### Introduction

- Comparing carbon nanotubes with our wish list for the "switch of the future"

- Bridging the gap: Show a strategy how to bring nanotubes into the semiconductor eco-system

- Conclusions

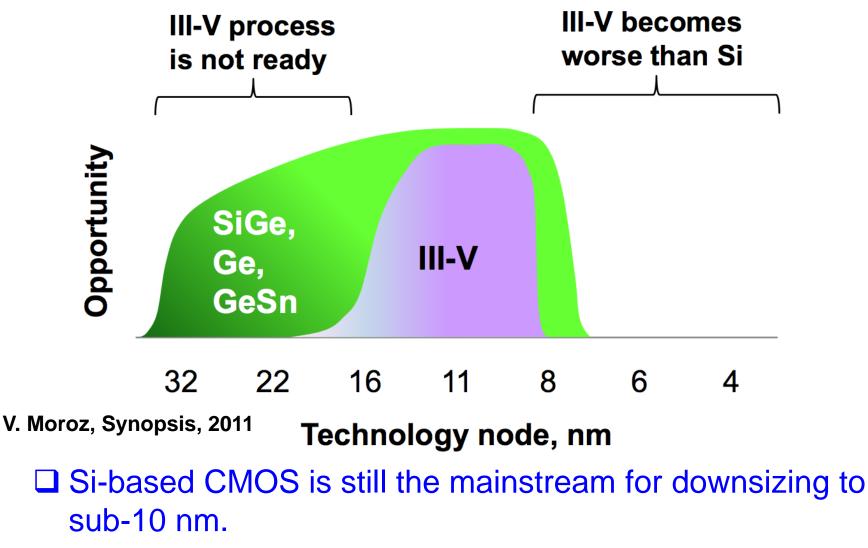

# Limited time window for alternatives

Technische Universität München

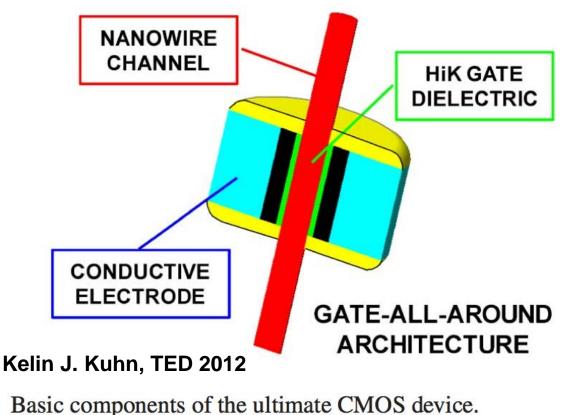

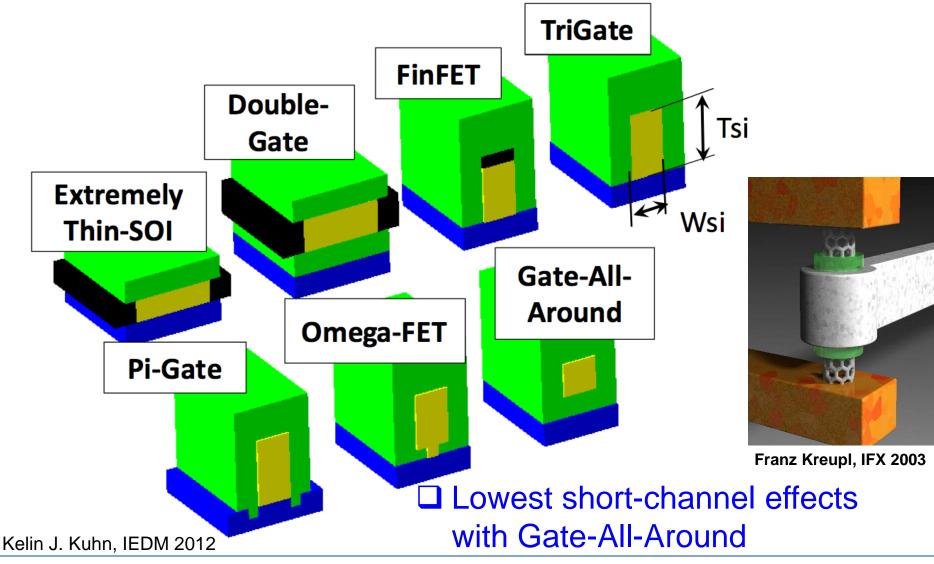

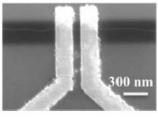

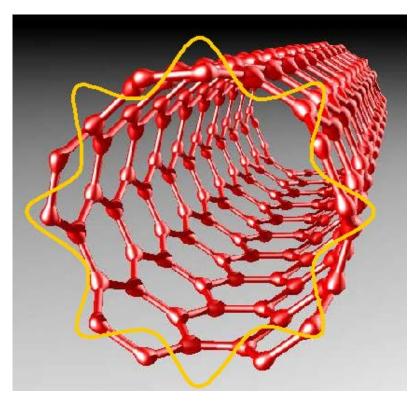

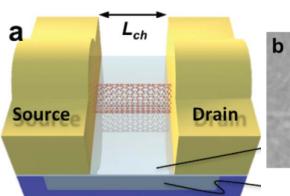

#### **Electrostatics favors gate-all-around**

#### Carbon nanotubes do gate-all-around

TaN

5 nm TaN

- 1 nm AlO<sub>x</sub>N<sub>y</sub> + 8 nm HfO<sub>2</sub>

work: Franklin et al., IEDM 2012 patent: Kreupl & Seidel US 7646045

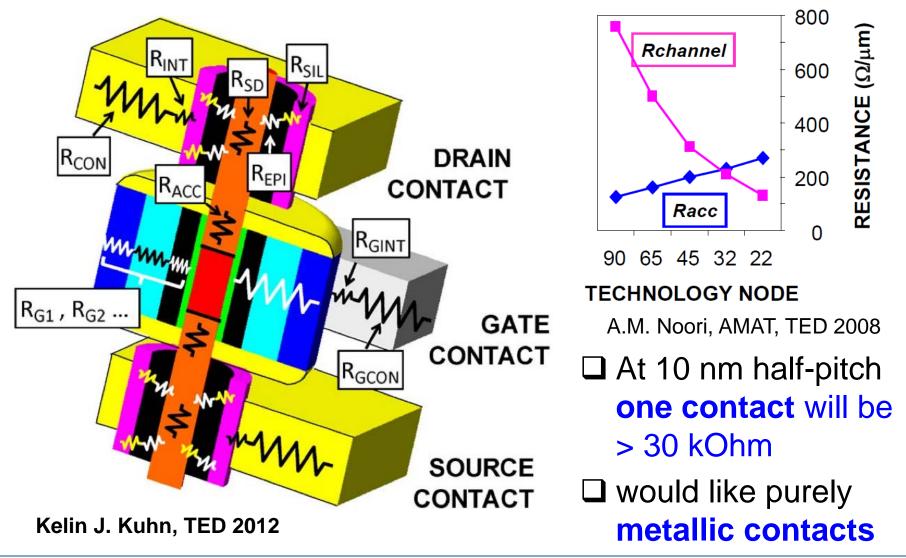

### **Contact resistance: major headache**

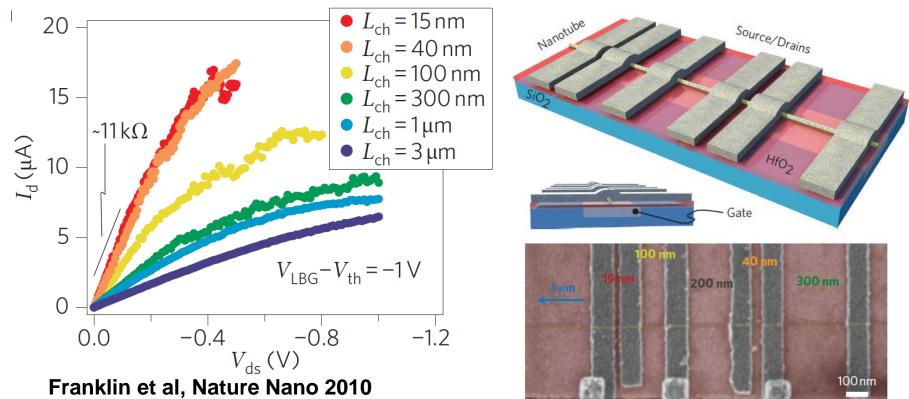

# Carbon nanotubes do have metallic S/D

One contact to 1 nm wide channel will be ~ 5.5 kOhm

Short channel (15-40 nm) operates in the ballistic limit

Type of metal defines p- or n-type channel

Department of Hybrid Electronic Systems

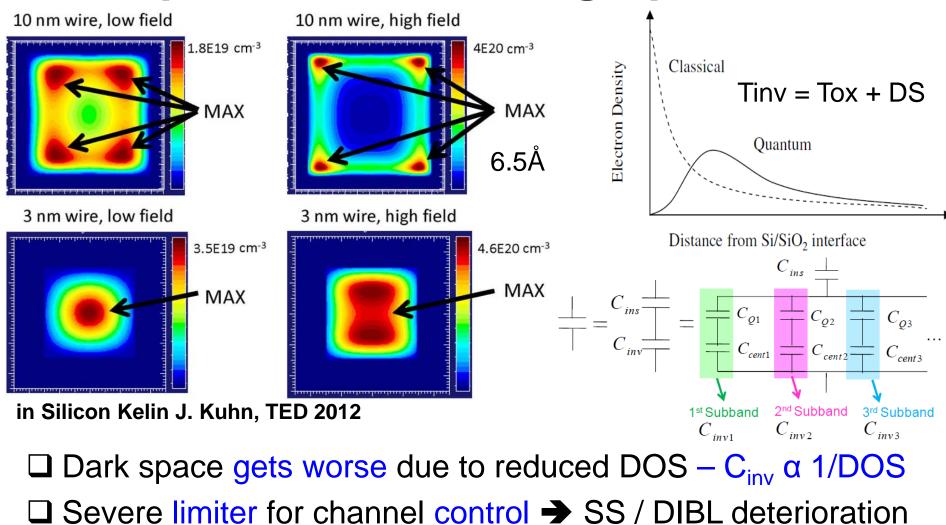

### Dark space in silicon / high-µ channels

Skotnicki & Boeuf, VLSI 2010

# **Carbon Nanotubes have no dark space**

- Current is confined to a single atomic layer

- Intimate channel control & low DOS

- Operation in the quantum capacitance limit (QCL) possible

- In QCL, the potential in channel is determined by the gate potential

- short channel effects are suppressed

□ Nanotube have no dopants

c.f. Knoch et al. EDL, 2008

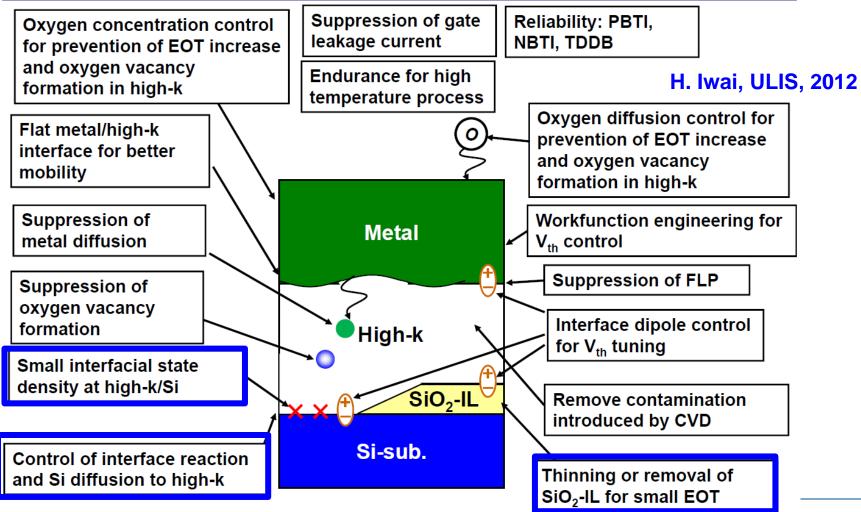

# **Channels need high-k compatibility**

#### Issues in high-k/metal gate stack

Technische Universität München

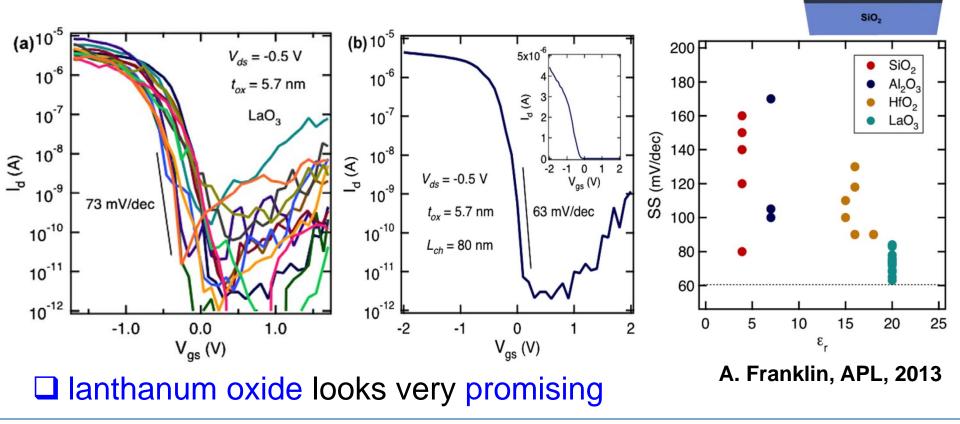

# **Carbon Nanotubes are high-k compatible**

# High-k materials are easily employed

LaO<sub>3</sub> Local Pd Gate

# Si performance vs L<sub>gate</sub> and voltage scaling

|                                      | Intel<br>(IEDM2007, 2009) |           | Intel<br>(VLSI2012) | Toshiba<br>(VLSI2012) | IBM<br>(VLSI2012) | Samsung<br>(IEDM2012) | IBM<br>(IEDM2009)    | STMicro.<br>(VLSI2008)      | Tokyo Tech<br>(ESSDERC2010) |  |

|--------------------------------------|---------------------------|-----------|---------------------|-----------------------|-------------------|-----------------------|----------------------|-----------------------------|-----------------------------|--|

| Structure                            | Bulk Planar               |           | Tri-Gate<br>22nm    | Tri-Gate NW           | ETSOI             | Bulk Planar           | GAA NW               | GAA NW                      | Ω-gate NW                   |  |

|                                      | 45nm 32nm                 |           |                     |                       |                   |                       |                      |                             |                             |  |

| L <sub>g</sub> (nm)                  | 35                        | 30        | 30                  | 14                    | 22                | 20                    | 35/25<br>(nFET/pFET) | 22/30<br>(nFET/pFET)        | 65                          |  |

| Gate<br>Dielectrics                  | Hf-based                  |           | Hf-based            | SiO <sub>2</sub>      | HfO <sub>2</sub>  | HfO <sub>2</sub> ?    | Hf-based             | lf-based HfZrO <sub>2</sub> |                             |  |

| EOT (nm)                             | 1                         | 0.95      | 0.9                 | 3                     | ~1                | -                     | 1.5                  | -                           | 3                           |  |

| V <sub>th</sub> (V)                  | ~0.4                      | ~0.3      | ~0.2                | -0.15 (nFET)          | 0.3~0.4           | ~0.3                  | 0.3~0.4              | ~0.5                        | -0.2 (nFET)                 |  |

| V <sub>DD</sub> (V)                  | 1                         | 1         | 0.8                 | 1                     | 1                 | 0.9                   | 1                    | 1.1                         | 1                           |  |

| l <sub>on</sub> (mA/um)<br>nFET/pFET | 1.36/1.07                 | 1.53/1.23 | 1.26/1.1            | 0.83 (nFET)           | 1.65/1.25         | 1.2/1.05              | 0.83/0.95            | 2.05/1.5                    | 1.32 (nFET)                 |  |

| DIBL<br>(mV/V)<br>nFET/pFET          | ~150                      | ~200      | 46/50               | <50                   | 75/130            | 104/115               | 65/105               | 56/9                        | 62                          |  |

| SS<br>(mV/dec)                       | -                         | ~100      | ~70                 | <80                   | <90               | 87                    | 85                   | <80<br>  <80                | ISCDG 201                   |  |

#### No data at low Vds (0.5V) and short Lgate

#### III-V/Ge benchmark – only long Lgate

|                            | Planar<br>(metal S/D, Strain, Buffer)      |                                                                                              | FinFET                                                |                                           | Tri-gate                     |                               | Gate-all-around<br>MOSFET                                         |                                                | Nanowire                           |                               |                                                 |

|----------------------------|--------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------|------------------------------|-------------------------------|-------------------------------------------------------------------|------------------------------------------------|------------------------------------|-------------------------------|-------------------------------------------------|

| material                   | InGaAs                                     | Ge                                                                                           | InGaSn                                                | InGaAs                                    | Ge                           | InGaAs                        | Ge                                                                | InGaAs                                         | Ge                                 | InGaAs<br>(multishell)        | Ge                                              |

| Dieletric<br>/EOT          | Al <sub>2</sub> O <sub>3</sub> /<br>3.5 nm | 7.6 A <sup>o</sup><br>HfO <sub>2</sub> +<br>Al <sub>2</sub> O <sub>3</sub> +GeO <sub>2</sub> | 5nm ALD<br>Al <sub>2</sub> O <sub>3</sub>             | 5nm ALD<br>Al <sub>2</sub> O <sub>3</sub> | SiON                         | 1.2 nm                        | 5.5 nm<br>(Al <sub>2</sub> O <sub>3</sub> +<br>GeO <sub>2</sub> ) | 10nm-<br>ALD<br>Al <sub>2</sub> O <sub>3</sub> | HfO <sub>2</sub> :<br>11nm         | HfAlO<br>14.8 nm              | 3.0 nm<br>(ALD Al <sub>2</sub> O <sub>3</sub> ) |

| Mobility                   | -                                          | ~600<br>(cm²/Vs)                                                                             | N <sub>s</sub> : 5e12<br>e: 200<br>h: 400<br>(cm²/Vs) | ~700<br><mark>(</mark> μS/μm <sub>)</sub> | -                            | -                             | -                                                                 | 701<br>(μS/μm)                                 | -                                  | ~500<br>(μS/μm)               | ~850<br>(cm²/Vs)                                |

| L <sub>ch</sub> (nm)       | 55                                         | W/L=<br>30/5 μm                                                                              | 50 µm                                                 | 100                                       | 4.5 μm                       | 60                            | 183                                                               | 50                                             | 200                                | 200                           | 65                                              |

| DIBL<br>(mV/V)             | 84                                         | -                                                                                            | -                                                     | 180                                       | -                            | ~50                           | -                                                                 | 210                                            | -<br>Iwai & (                      | -<br>Salvo, ISC               | -                                               |

| SS<br>(mV/dec)             | 105                                        | -                                                                                            | 150K<br>61pMOS<br>33nMOS<br>120K                      | 145                                       | 750                          | 90                            | 130                                                               | 150                                            | 160                                | -                             | -                                               |

| l <sub>on</sub><br>(μΑ/μm) | 278<br>(V <sub>D</sub> =0.5V)              | 3<br>(V <sub>D</sub> =-0.2V)                                                                 | 4 (n,p)<br>(V <sub>D</sub> =0.5V)                     | -                                         | 10<br>(V <sub>D</sub> =0.5V) | 400<br>(V <sub>D</sub> =0.5V) | 235<br>(V <sub>D</sub> =-1V)                                      | 180<br>(V <sub>D</sub> =0.5V)                  | 604<br>(V <sub>D</sub> =-0.5V)     | 100<br>(V <sub>D</sub> =0.5V) | 731<br>(V <sub>D</sub> =-1V)                    |

| Research<br>Group          | Tokyo Uni<br>VLSI 2012                     | Tokyo Uni<br>VLSI 2012                                                                       | Stanford<br>Uni VLSI<br>2012                          | Purdue<br>Uni IEDM<br>2009                | Stanford<br>Uni ELD<br>2007  | Intel<br>IEDM<br>2011         | NNDL<br>Taiwan<br>IEDM 2011                                       | Purdue<br>Uni IEDM<br>2011                     | ASTAR<br>Singapore<br>IEDM<br>2009 | Hokkaido<br>Uni, IEDM<br>2011 | AIST<br>Tsukuba<br>VLSI 2012<br>31              |

#### No data at low Vds (0.5V) and short Lgate

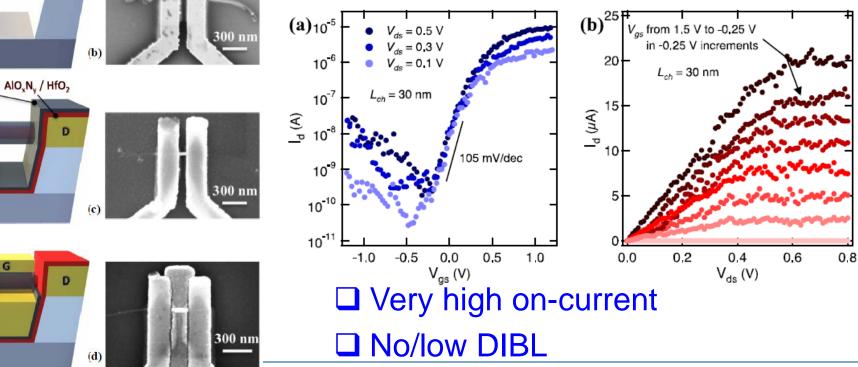

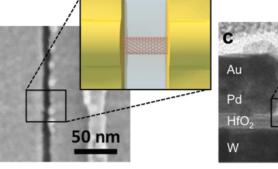

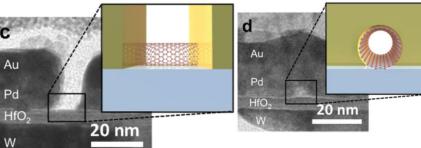

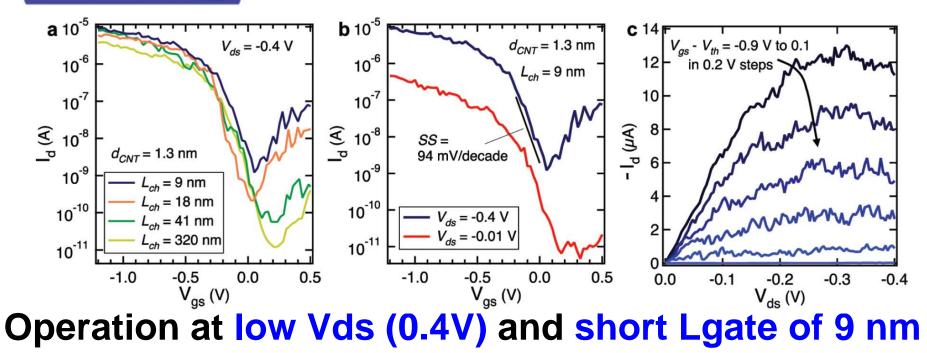

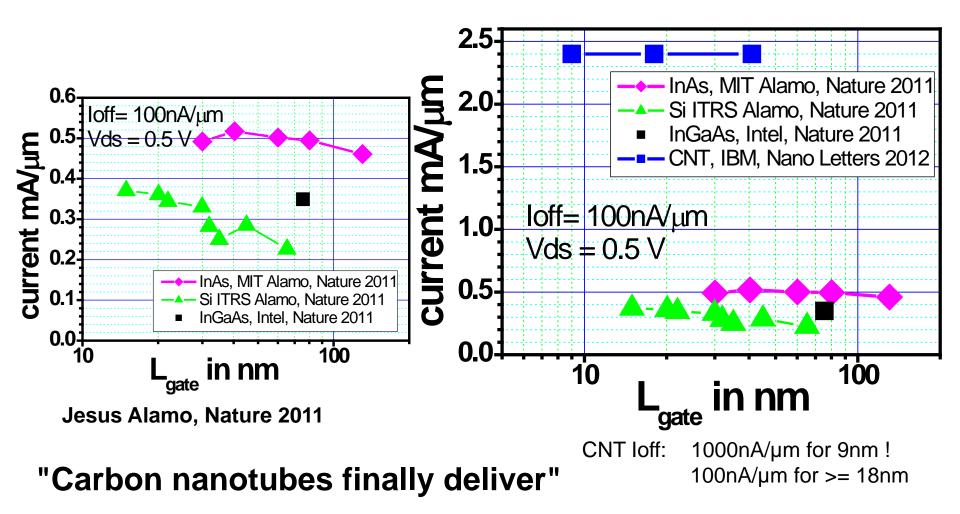

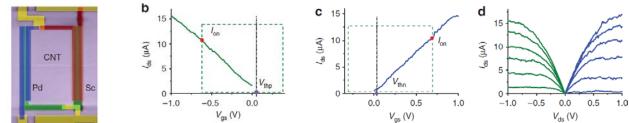

#### Sub-10 nm carbon nanotube transistor

Franklin, Nano Letters 2012

#### **Carbon nanotubes outperform alternatives**

(PTL),

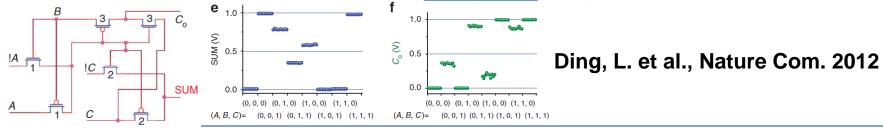

# Advantage for CNTs in circuit designs

❑ CNT-based ICs can be designed as pass-transistor logic

- Drawback of conventional Si-based PTL circuits—threshold voltage drop—is avoided in CNT PTL circuits

- Threshold voltage can be adjusted close to zero for p- and n-CNT FET (operation at Vdd= 1 and 0.4 V demoed)

- number of FETs & power greatly reduced / enhanced speed

- □ Full adder: instead of 28 FETs (in Si) only 6 CNT FETs

# **Great News – how to proceed?**

- Please give instructions

- how to place billions of nanotubes with

- one type of chirality

- equal length

- on a substrate

- well aligned at some nanometer pitch

- with a throughput of 120 wafers per hour

■ Solution: Just issue a purchase order for the new Applied Materials *Nano-Wonder<sup>TM</sup>* machine No - unfortunately – I am kidding

#### Grow in place or transfer

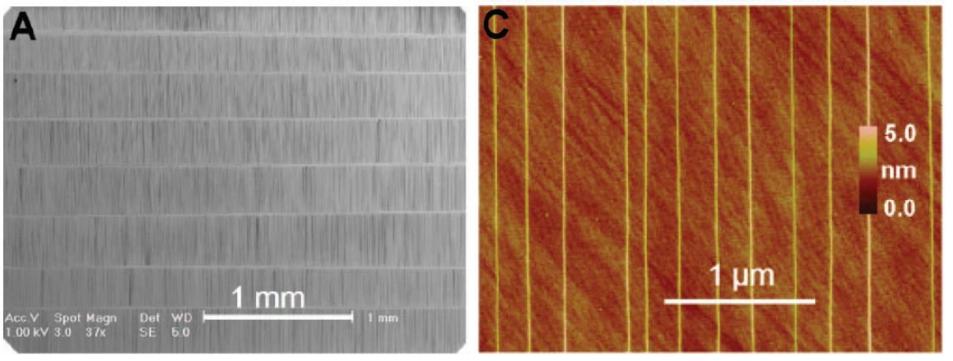

95 % semiconducting CNTs possible (Lei Ding et al, NL 2009)

#### □ aligned growth is possible – pitch not (yet) suitable

#### Grow in place or transfer

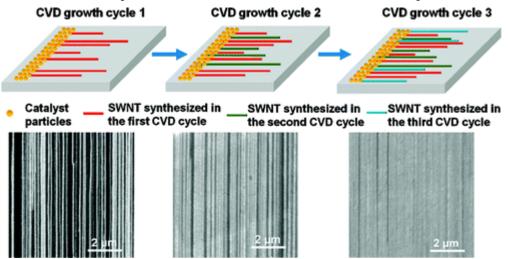

#### density can be increased by multiple growth

W Zhou et al., J. ACS Nano, 2011

#### □ Would work if growth length is > 300 /450 mm

- □ Longest grown nanotube is 18.5 cm

- Metallic could be eliminated (new methods)

- Poor control over chirality

Xueshen Wang et al, Nano Let. 2009

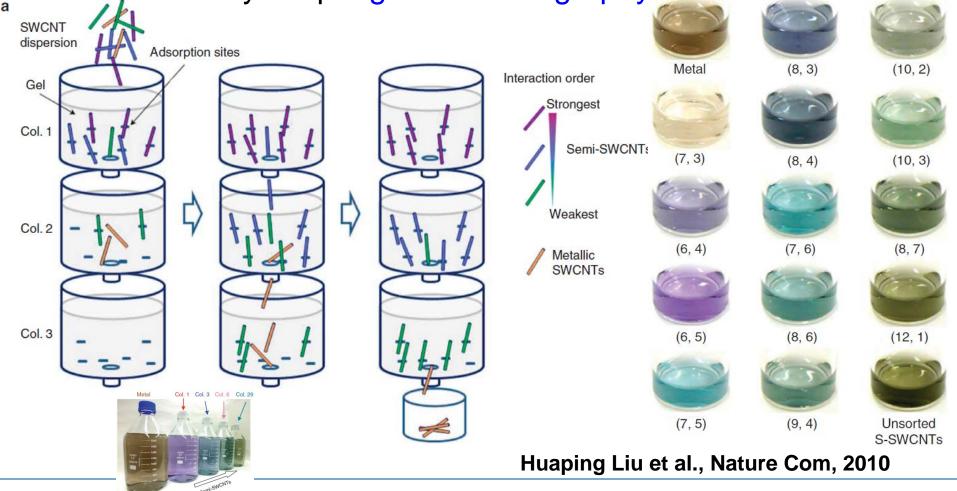

- □ Use **self-assembly** to place nanotube

- □ Key ingredient: only semiconducting nanotubes

- Bulk produced single-walled nanotubes (HiPCo etc)

- Large-scale single-chirality separation of single-wall carbon nanotubes by simple gel chromatography or density gradient or DNA methods

- □ cloning of specific chirality may be omitted

- Develop a site specific selective binding to deposit nanotubes at specific location

- □ Start integration work / fabrication of the devices

- Evaluate (millions of) devices

- □ Feedback and improve process start again

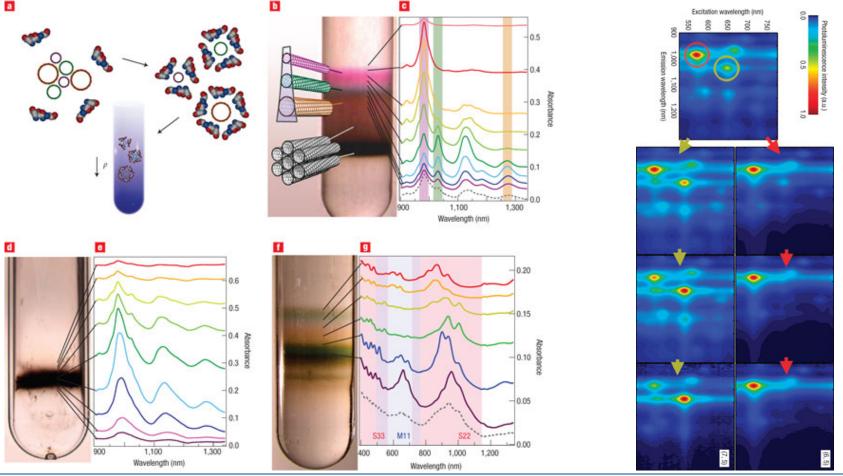

Large-scale single-chirality separation of single-wall carbon nanotubes by simple gel chromatography

□ Single-chirality separation of single-wall carbon nanotubes

by density gradient Michael S. Arnold et al., Nature Nano, 2006

DNA sequence for structure-specific separation of carbon nanotubes.

X. M. Tu et al., Nature 2009

#### Table 2 | Experimental conditions and quantification

| Chirality<br>(n,m) | Sequence                 | Dispersion solution*        | Incubation period† | Yield‡<br>(μg per 100 μg) | Purity§<br>(%) |  |

|--------------------|--------------------------|-----------------------------|--------------------|---------------------------|----------------|--|

| (9,1)              | (TCC) <sub>10</sub>      | 0.1 M NaCl                  | None               | 0.1                       | 80             |  |

| (8,3)              | (TTA) <sub>3</sub> TTGTT | 0.1 M NaCl                  | 1 day              | 0.1                       | 70             |  |

| (6,5)              | $(TAT)_4$                | 0.1 M NaCl                  | None               | 0.5                       | 90             |  |

| (7,5)              | (ATT) <sub>4</sub> AT    | 0.1 M NaCl                  | None               | 0.2                       | 90             |  |

| (10,2)             | (TATT) <sub>2</sub> TAT  | 0.1 M NaCl                  | None               | 0.1                       | 90             |  |

| (8,4)              | (ATTT) <sub>3</sub>      | 0.1 M NaCl                  | None               | 0.3                       | 90             |  |

| (9,4)              | (GTC) <sub>2</sub> GT    | 0.1 M sodium acetate pH 4.5 | 2 days             | 0.5                       | 60             |  |

| (7,6)              | (GTT) <sub>3</sub> G     | 0.1 M NaCl                  | None               | 0.4                       | 90             |  |

| (8,6)              | (GT) <sub>6</sub>        | 0.1 M NaCl                  | 1 day              | 0.8                       | 90             |  |

| (9,5)              | (TGTT) <sub>2</sub> TGT  | 0.1 M NaCl, 10% glycerol    | None               | 0.3                       | 70             |  |

| (10,5)             | (TTTA) <sub>3</sub> T    | 0.1 M sodium acetate pH 4.5 | 2 days             | 0.5                       | 90             |  |

| (8,7)              | (CCG) <sub>2</sub> CC    | 0.1 M NaCl, 10% glycerol    | None               | 0.4                       | 80             |  |

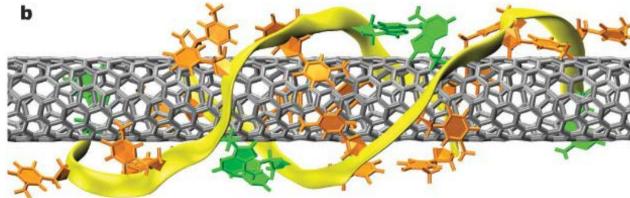

Cloning of a specific chirality

Jia Liu et al., Nature Com 2012

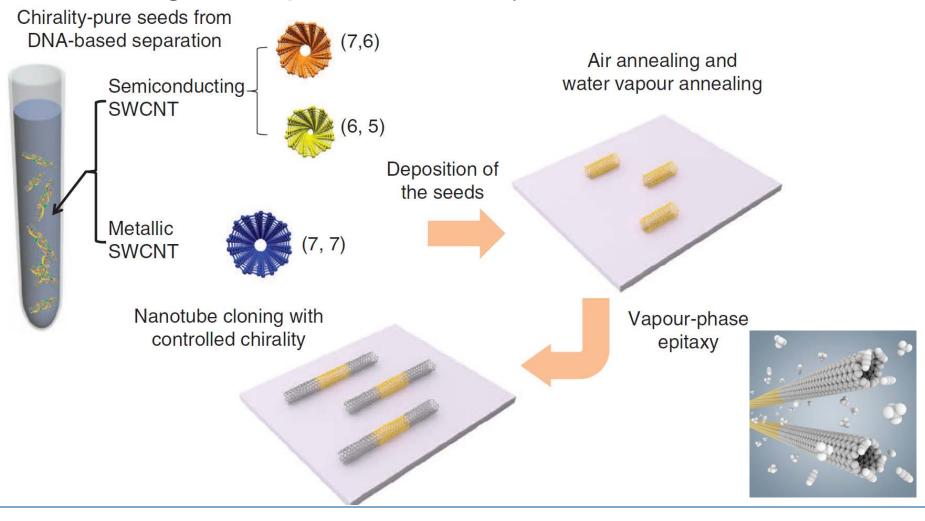

# Placement strategies Hongsik Park et al., Nature Nano 2012

□ Site specific selective binding to deposit nanotubes

■ Site specific selective binding to deposit nanotubes

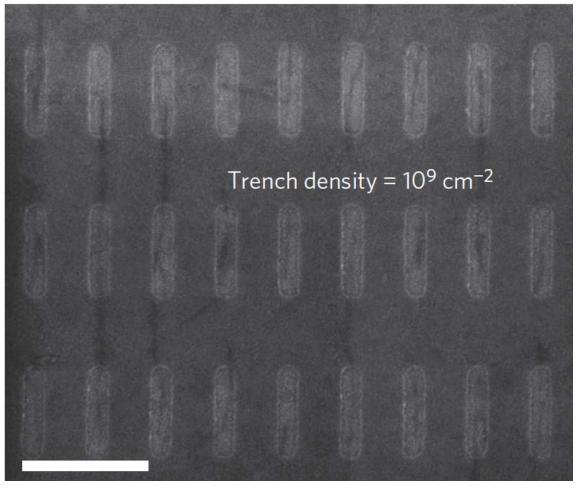

□ 200 nm pitch in the x-direction **500** nm pitch in the y-direction □ 10<sup>9</sup> sites/cm<sup>2</sup> density (scale bar, 400 nm). precise placement in two dimensions □ 90% of the trenches contain at least one nanotube

#### Placement strategies Hongsik Park et al., Nature Nano 2012

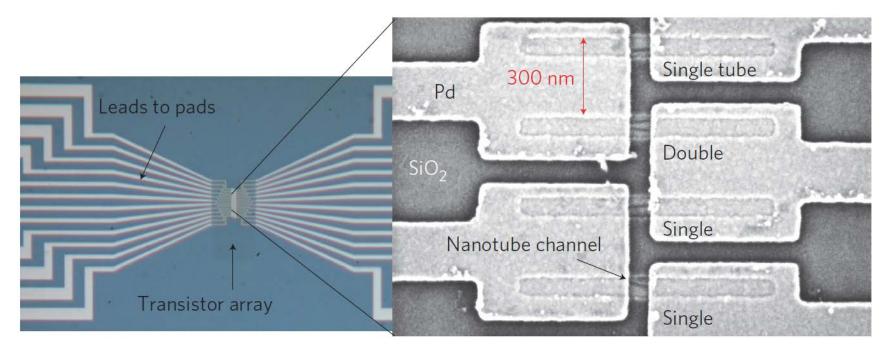

#### □ Fabricate devices at the CNT-filled trenches

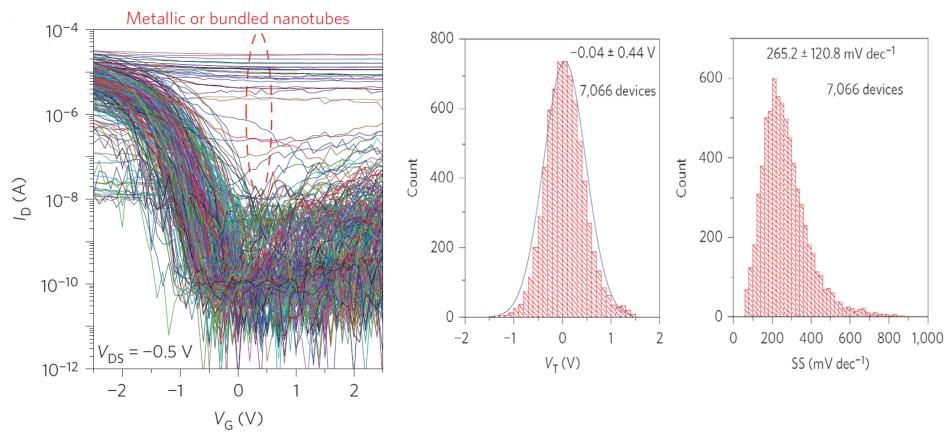

More than 10,000 devices have been fabricated over the pre-patterned trenches with CNT-selfassembly by ion-exchange reaction

#### **Placement strategies** Hongsik Park et al., Nature Nano 2012 **Evaluation** of more than 10,000 CNT devices

This is an amazing result – given that 2 people have worked on the topic for a couple of month

B B Department of Hybrid Electronic Systems

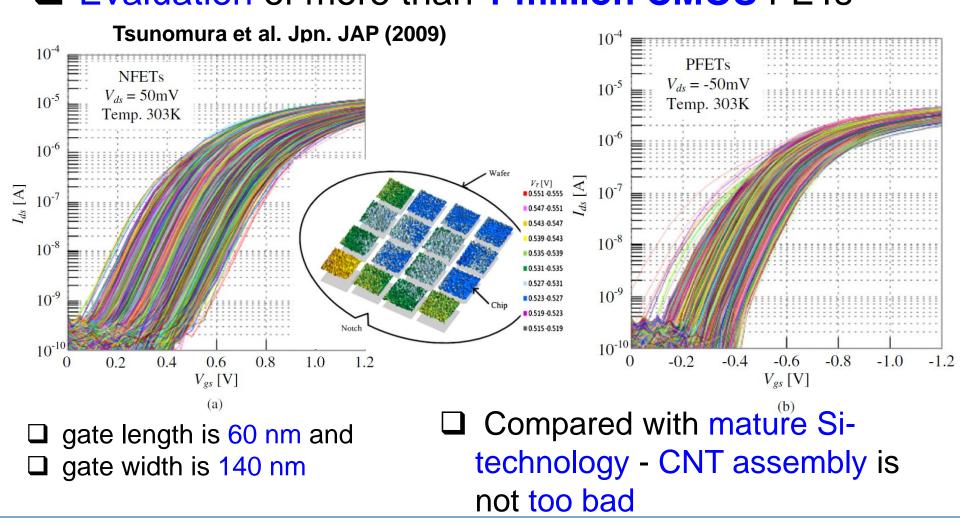

#### **Just compare – for a moment - with Si Evaluation** of more than **1 million CMOS** FETs

#### Summary

- Opportunity window for alternative channel materials is closing

- Performance-wise carbon nanotube devices outperform any alternative

- Huge gap for industrial integration exists

- A possible roadmap exists based on self-assembly

- The low-hanging fruits for nanotube device research are gone

- What remains is hard work to make it happen – not ideally suited for academia